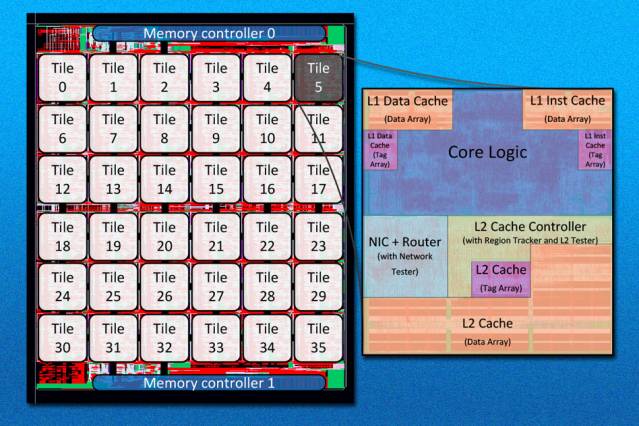

Design lets chip manage local memory stores efficiently using an Internet-style communication network.

The more cores — or processing units — a computer chip has, the bigger the problem of communication between cores becomes. For years, Li-Shiuan Peh, the Singapore Research Professor of Electrical Engineering and Computer Science at MIT, has argued that the massively multicore chips of the future will need to resemble little Internets, where each core has an associated router, and data travels between cores in packets of fixed size.

This week, at the International Symposium on Computer Architecture, Peh’s group unveiled a 36-core chip that features just such a “network-on-chip.” In addition to implementing many of the group’s earlier ideas, it also solves one of the problems that has bedeviled previous attempts to design networks-on-chip: maintaining cache coherence, or ensuring that cores’ locally stored copies of globally accessible data remain up to date.

Read more . . .

The Latest on: Multicore chips

[google_news title=”” keyword=”Multicore chips” num_posts=”10″ blurb_length=”0″ show_thumb=”left”]

via Google News

The Latest on: Multicore chips

- The best laptops for video editing, according to an experienced editoron April 27, 2024 at 2:00 am

With so many laptops offering wildly different features, it's important to narrow down which ones matter the most. In McQuaid's opinion, there are three qualities that a good video editing laptop ...

- The MacBook Pro might finally have some competition as Microsoft's Qualcomm X Elite-powered Surface Laptop 6's benchmarks leakon April 26, 2024 at 11:15 am

To put the figures into perspective, an M3 Pro 14-inch MacBook Pro scores 3,125 in single-core and 15,124 in multi-core tests while the larger 16-inch MacBook Pro manages scores that are almost ...

- Snapdragon X Elite Surfaces on Geekbench, Beats Apple's M3 Chip in Multi-Core Teston April 26, 2024 at 1:01 am

Microsoft's purported Surface Laptop 6 with a Snapdragon X Elite chip has a single-core score of 2,714 points, and a multi-core score of 14,078 points.

- Qualcomm says lower-end Snapdragon X Plus chips can still outrun Apple’s M3on April 25, 2024 at 5:26 am

Ahead of the chips' launch late this year, Qualcomm announced a new lower-end model destined for cheaper devices. Dubbed the Snapdragon X Plus, it shares a lot in common with the flagship Snapdragon X ...

- Qualcomm Snapdragon X Plus Sets Efficient Performance Bar In New Benchmarkson April 24, 2024 at 2:39 pm

Suffice it to say that Qualcomm’s Snapdragon X Elite and X Plus impact in the market will be much more significant than its previous-gen PC platforms.

- First Look: Qualcomm Is Coming for Intel’s Lunch With the Snapdragon X Pluson April 24, 2024 at 10:46 am

The ARM-based chips will come to PCs soon, but they’re promising AI performance that might finally see AI run on your PC, and not the cloud.

- Qualcomm strong-arms its way into Windows laptops this summeron April 24, 2024 at 10:00 am

The Snapdragon X Plus is Qualcomm’s entry-level laptop chip. It has 10 cores, 42MB of cache, a maximum multithreaded frequency of 3.4GHz, and an NPU with 45 tera operations per ...

- New Qualcomm Snapdragon X Plus SoC for Windows Arm Laptops Benchmarkedon April 24, 2024 at 9:51 am

Qualcomm is pulling the wraps off a previously secret Snapdragon X SoC for Windows. It had previously announced the X Elite, and now it's officially unveiling a slightly cut-down version named X Plus.

- Even the new mid-tier Snapdragon X Plus beats Apple’s M3on April 24, 2024 at 6:00 am

Qualcomm is expanding its PC portfolio with the new Snapdragon X Plus chip, which is 10% faster than the Apple M3, and 37% faster than Intel's Core Ultra CPUs.

- Qualcomm is expanding its next-gen laptop chip line with the Snapdragon X Pluson April 24, 2024 at 6:00 am

Ahead of the Snapdragon X Elite's arrival later this year, today Qualcomm announced a second laptop processor based on its Oryon CPU architecture.

via Bing News