Stanford researchers are building layers of logic and memory into skyscraper chips that are smaller, faster, cheaper – and taller

For decades, the mantra of electronics has been smaller, faster, cheaper.

Today, Stanford engineers add a fourth word – taller.

At a conference in San Francisco, a Stanford team will reveal how to build high-rise chips that could leapfrog the performance of the single-story logic and memory chips on today’s circuit cards.

Those circuit cards are like busy cities in which logic chips compute and memory chips store data. But when the computer gets busy, the wires connecting logic and memory can get jammed.

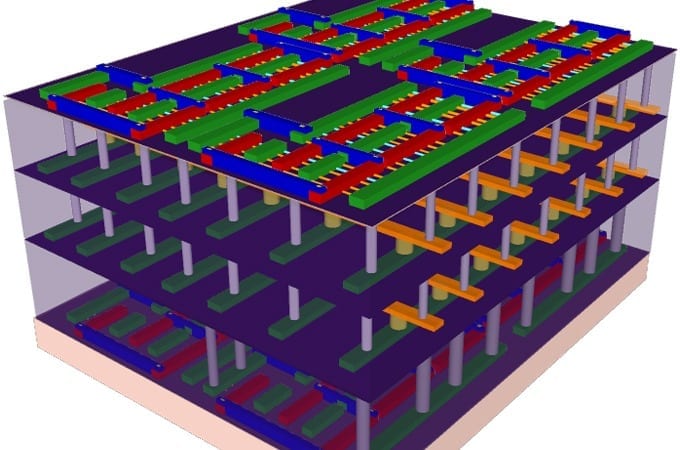

The Stanford approach would end these jams by building layers of logic atop layers of memory to create a tightly interconnected high-rise chip. Many thousands of nanoscale electronic “elevators” would move data between the layers much faster, using less electricity, than the bottleneck-prone wires connecting single-story logic and memory chips today.

The work is led by Subhasish Mitra, a Stanford associate professor of electrical engineering and of computer science, and H.-S. Philip Wong, the Williard R. and Inez Kerr Bell Professor in Stanford’s School of Engineering and a professor of electrical engineering. They describe their new high-rise chip architecture in a paper being presented at the IEEE International Electron Devices Meeting (IEDM) on Dec. 15-17.

The researchers’ innovation leverages three breakthroughs.

The first is a new technology for creating transistors, those tiny gates that switch electricity on and off to create digital zeroes and ones. The second is a new type of computer memory that lends itself to multistory fabrication. The third is a technique to build these new logic and memory technologies into high-rise structures in a radically different way than previous efforts to stack chips.

“This research is at an early stage, but our design and fabrication techniques are scalable,” Mitra said. “With further development this architecture could lead to computing performance that is much, much greater than anything available today.”

Wong said the prototype chip to be unveiled at IEDM shows how to put logic and memory together into three-dimensional structures that can be mass-produced.

“Paradigm shift is an overused concept, but here it is appropriate,” Wong said. “With this new architecture, electronics manufacturers could put the power of a supercomputer in your hand.”

Read more: Stanford Team Combines Logic, Memory to Build a ” High-Rise” Chip

The Latest on: High-rise chip

[google_news title=”” keyword=”High-rise chip” num_posts=”10″ blurb_length=”0″ show_thumb=”left”]

via Google News

The Latest on: High-rise chip

- To put bloom back on UCLA, new coach DeShaun Foster and staff rip up Chip Kelly's blueprinton April 30, 2024 at 11:54 am

In the two months since Chip Kelly left the building on his way to Ohio State, the Bruins have charted a different path ...

- Samsung's operating profit soars 930% as AI tailwinds drive demand for memory chipson April 30, 2024 at 9:04 am

Samsung Electronics said on Tuesday that its operating profit surged more than 930% in the first quarter of 2024, driven by soaring demand for its servers, memory chips and storage used in AI ...

- FTSE 100 Live 30 April: No record close as index finishes down three points, US stocks downon April 30, 2024 at 8:40 am

In the first quarter of the year HSBC made profit of $12.7 billion. That is down 1.8%, but better than City analysts had expected. It will buy back another $3 billion of shares.HSBC shares rose 1p to ...

- Forget Nvidia: Prominent Billionaires Are Selling It and Buying These 2 Ultra-High-Yield Dividend Stocks Insteadon April 30, 2024 at 2:06 am

Wall Street's brightest, most successful billionaire money managers are ditching Nvidia in favor of two time-tested income stocks with yields of 6.6%!

- FTSE 100 Live 30 April: HSBC boss in surprise retirement, Whitbread cuts jobs, blue-chips rise againon April 30, 2024 at 12:16 am

Change at the top of HSBC and the performance of Premier Inn owner Whitbread are among today’s City talking points. Noel Quinn surprised HSBC investors by announcing plans for his departure after ...

- Samsung Profit Soars Tenfold As Chip Demand Rebounds Amid AI Boomon April 29, 2024 at 9:27 pm

Samsung Electronics reports a staggering surge in earnings amid chip market recovery and strong demand for AI-enabled smartphones.

- These ASX 200 blue chip shares could rise 20% to 30%on April 29, 2024 at 4:53 pm

These ASX 200 blue chip shares could be great options for investors according to one leading broker. Here's what it is ...

- Samsung First-Quarter Profit up 10-Fold on Memory Chip Recoveryon April 29, 2024 at 4:52 pm

SEOUL (Reuters) - Samsung Electronics reported on Tuesday a more than 10-fold rise in its first-quarter operating profit, as memory chip prices rose steeply from a severe downturn thanks in part to a ...

- Gangs forced out Haiti’s government. This FBI ‘Most Wanted’ gang leader claims they’re liberating the countryon April 29, 2024 at 2:00 am

A day with the notorious accused kidnapper Vitelhomme Innocent, whose armed group Kraze Baryé is among the allied gangs terrorizing the Caribbean nation.

- Futures Rise as Chip Stocks Bounce Back After Sell-Offon April 18, 2024 at 3:02 am

(Reuters) - Futures for the S&P 500 and the Nasdaq gained on Thursday as some chip stocks recouped losses after a sell-off, while investors awaited Federal Reserve policymakers' stance on ...

via Bing News