It is time for computer designers to work smart instead of strong, which is just what Devadas is doing.

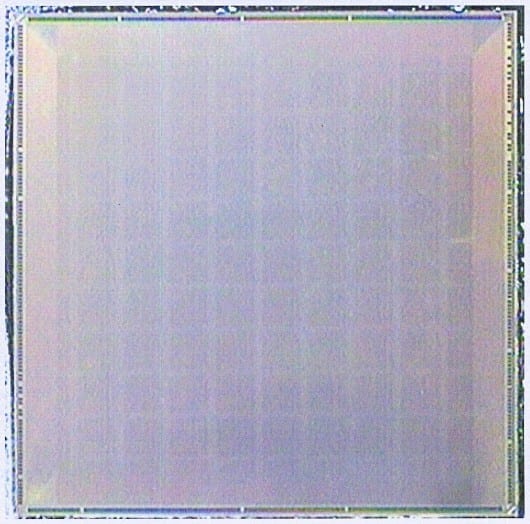

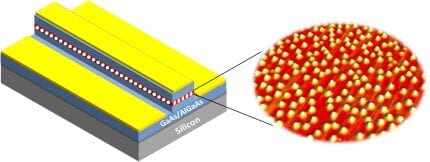

Computer scientists at MIT have developed a 110-core CPU chip based on a new architecture in which, instead of bringing data across the chip to the core that happens to want it, the program is moved to the core where the data is stored. In practice, this new architecture reduces the amount of on-chip data exchange tenfold, along with cutting the heat and infrastructure demanded by conventional chip architecture.

You may have noticed that the rapid progress of computing power has become a bit sluggish in the past decade or so. While Moore’s law is still intact, clock speeds have stalled at about 4 GHz, instead of the 50 GHz we would now have achieved based on historical rates of increase.

Multiple-core chips are commonly used to increase peak computing speeds, but run into problems with overheating as data is shuffled back and forth between the cores. MIT professor Srinivas Devadas offers a path to increased computing power by instead moving the program to a core having direct access to the required data.

The number of transistors (MOSFETs – Metal Oxide Silicon Field Effect Transistors) that can be integrated onto a single chip continues to double about every two years, as the feature size of lithographic process technology shrinks. However, Moore’s law, as this is called, is only one part of why computing power has grown so rapidly.

The other part is Dennard scaling, which describes how the performance of the MOSFETs scale with decreasing feature size.

Go deeper with Bing News on:

CPU chip architecture

- Chinese chipmaker Loongson's new 3B6600 and 3B7000 chips narrow performance gap with Intel and AMD offerings

Its new graphics architecture will support OpenGL 4.0 ... Last year saw the launch of Loongson's 3A6000 chip, a quad-core CPU at 2.5GHz. Performance benchmarks from a Chinese testing agency ...

- Huawei Leaks: Next-Gen Kirin CPU to Rival Apple's M3 Processor

Huaweis chip development team is rumored to be working on a next-generation Kirin CPU that could give Apples M3 a run for its money. The chip is expected to leverage the innovative Taishan V130 ...

- What is CPU cache, and why is it so important for gaming?

CPU cache can have a big affect on processor and system performance. But what is cache, and what does it do? Read on to find out.The Latest Tech News, Delivered to Your Inbox ...

- Pentium 4 – the CPU Intel got SO wrong

Huge clock speeds, hot temperatures, and disappointing performance. We look at the catastrophically misjudged Intel NetBurst architecture.

- Qualcomm says lower-end Snapdragon X Plus chips can still outrun Apple’s M3

Ahead of the chips' launch late this year, Qualcomm announced a new lower-end model destined for cheaper devices. Dubbed the Snapdragon X Plus, it shares a lot in common with the flagship Snapdragon X ...

Go deeper with Google Headlines on:

CPU chip architecture

[google_news title=”” keyword=”CPU chip architecture” num_posts=”5″ blurb_length=”0″ show_thumb=”left”]

Go deeper with Bing News on:

CPU chip

- New rumor that iPad Pros could launch with M4 chip on May 7, but we don't buy it

A new rumor from a prominent source says that Apple could speed-launch the Apple M4 chip with the iPad Pros on May 7, but we don't think so.

- Chinese chipmaker Loongson's new 3B6600 and 3B7000 chips narrow performance gap with Intel and AMD offerings

TechSpot means tech analysis and advice you can trust. In brief: Beijing was the setting for some bold claims from Loongson this week about its homegrown processor lineup. The Chinese tech firm says ...

- Huawei Leaks: Next-Gen Kirin CPU to Rival Apple's M3 Processor

Huaweis chip development team is rumored to be working on a next-generation Kirin CPU that could give Apples M3 a run for its money. The chip is expected to leverage the innovative Taishan V130 ...

- Huawei launches another 7nm processor built by sanctioned Chinese fab SMIC — Kirin 9010 builds on previous design

Despite efforts of U.S. government, HiSilicon continues to develop high-end SoCs and SMIC continues to make them.

- 14 Ways To Use A Food Processor You've Probably Never Thought Of

Your food processor is so much more than just a fancy blender. It can save you lots of time and cleanup for a variety of dishes you likely never imagined.

Go deeper with Google Headlines on:

CPU chip

[google_news title=”” keyword=”CPU chip” num_posts=”5″ blurb_length=”0″ show_thumb=”left”]